[CPU] SpeedStep의 진실과 SSDT, 그리고 잠자기에 관하여 [중]

[CPU] SpeedStep의 진실과 SSDT, 그리고 잠자기에 관하여 [중]

-

KsJ

KsJ - 1532

- 15

KsJ님의 기기정보

바로 1편을 작성하고 2편을 작성해봅니다 ㅎㅎㅎ...

시간이 있을 때, 그리고 그간 작성을 하도 못하다보니... 밀린걸 다 처리한다는 느낌이

생각보다 많이 들긴 합니다만, 그래도 전 계속 적으려 합니다. (헣헣)

요번편은 SSDT를 아에 통째로 복붙해넣고 다 뜯어보도록 할겁니다.... 글이 길어질 수 있으니!

주의 부탁드리도록 하겠습니다 :)

/*

* Intel ACPI Component Architecture

* AML Disassembler version 20140210-00 [Feb 10 2014]

* Copyright (c) 2000 - 2014 Intel Corporation

*

* Original Table Header:

* Signature "SSDT"

* Length 0x0000036A (874)

* Revision 0x01

* Checksum 0x00

* OEM ID "APPLE "

* OEM Table ID "CpuPm"

* OEM Revision 0x00017600 (95744)

* Compiler ID "INTL"

* Compiler Version 0x20140210 (538182160)

*/

DefinitionBlock ("ssdt.aml", "SSDT", 1, "APPLE ", "CpuPm", 0x00017600)

{

External (\_PR.CPU4, DeviceObj)

External (\_PR.CPU5, DeviceObj)

External (\_PR.CPU6, DeviceObj)

External (\_PR.CPU7, DeviceObj)

Scope (\_PR.CPU4)

{

Method (_INI, 0, NotSerialized)

{

Store ("ssdtPRGen version....: 17.6 / Mac OS X 10.11.3 (15D21)", Debug)

Store ("custom mode..........: 0", Debug)

Store ("host processor.......: Intel(R) Core(TM) i5-4670 CPU @ 3.40GHz", Debug)

Store ("target processor.....: i5-4670", Debug)

Store ("number of processors.: 1", Debug)

Store ("baseFrequency........: 800", Debug)

Store ("frequency............: 3400", Debug)

Store ("busFrequency.........: 100", Debug)

Store ("logicalCPUs..........: 4", Debug)

Store ("maximum TDP..........: 84", Debug)

Store ("packageLength........: 31", Debug)

Store ("turboStates..........: 4", Debug)

Store ("maxTurboFrequency....: 3800", Debug)

Store ("machdep.xcpm.mode....: 1", Debug)

}

Name (APLF, Zero)

Name (APSN, 0x04)

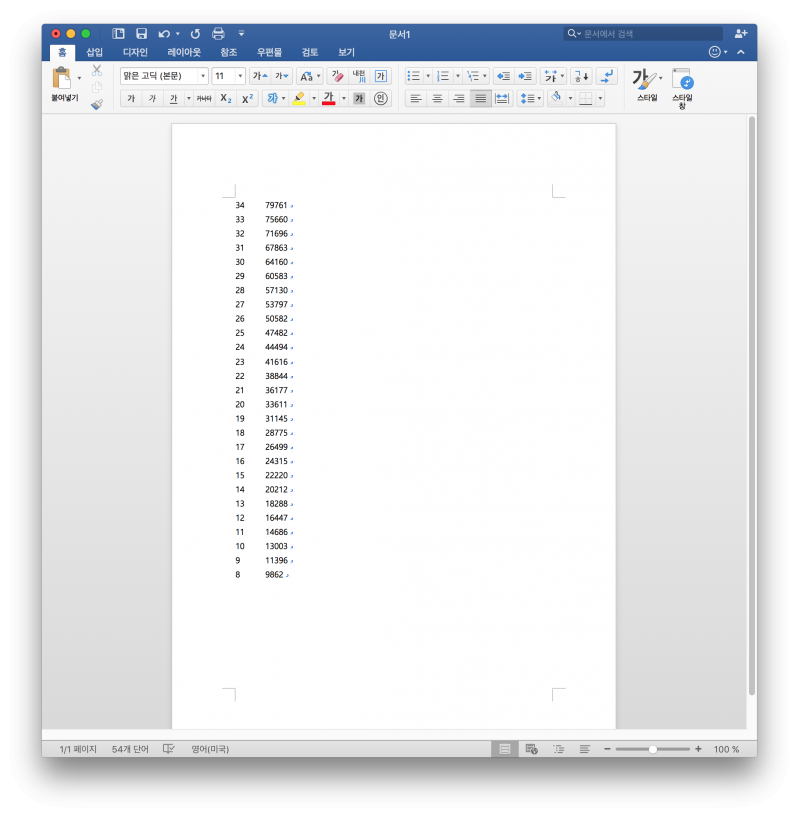

Name (APSS, Package (0x1F)

{

/* High Frequency Modes (turbo) */

Package (0x06) { 0x0ED8, 0x014820, 0x0A, 0x0A, 0x2600, 0x2600 },

Package (0x06) { 0x0E74, 0x014820, 0x0A, 0x0A, 0x2500, 0x2500 },

Package (0x06) { 0x0E10, 0x014820, 0x0A, 0x0A, 0x2400, 0x2400 },

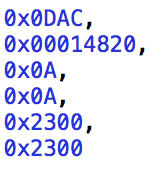

Package (0x06) { 0x0DAC, 0x014820, 0x0A, 0x0A, 0x2300, 0x2300 },

/* High Frequency Modes (non-turbo) */

Package (0x06) { 0x0D48, 0x014820, 0x0A, 0x0A, 0x2200, 0x2200 },

Package (0x06) { 0x0CE4, 0x013ADD, 0x0A, 0x0A, 0x2100, 0x2100 },

Package (0x06) { 0x0C80, 0x012DD8, 0x0A, 0x0A, 0x2000, 0x2000 },

Package (0x06) { 0x0C1C, 0x01210F, 0x0A, 0x0A, 0x1F00, 0x1F00 },

Package (0x06) { 0x0BB8, 0x011482, 0x0A, 0x0A, 0x1E00, 0x1E00 },

Package (0x06) { 0x0B54, 0x010831, 0x0A, 0x0A, 0x1D00, 0x1D00 },

Package (0x06) { 0x0AF0, 0x00FC1C, 0x0A, 0x0A, 0x1C00, 0x1C00 },

Package (0x06) { 0x0A8C, 0x00F041, 0x0A, 0x0A, 0x1B00, 0x1B00 },

Package (0x06) { 0x0A28, 0x00E4A0, 0x0A, 0x0A, 0x1A00, 0x1A00 },

Package (0x06) { 0x09C4, 0x00D939, 0x0A, 0x0A, 0x1900, 0x1900 },

Package (0x06) { 0x0960, 0x00CE0B, 0x0A, 0x0A, 0x1800, 0x1800 },

Package (0x06) { 0x08FC, 0x00C316, 0x0A, 0x0A, 0x1700, 0x1700 },

Package (0x06) { 0x0898, 0x00B859, 0x0A, 0x0A, 0x1600, 0x1600 },

Package (0x06) { 0x0834, 0x00ADD4, 0x0A, 0x0A, 0x1500, 0x1500 },

Package (0x06) { 0x07D0, 0x00A387, 0x0A, 0x0A, 0x1400, 0x1400 },

Package (0x06) { 0x076C, 0x009970, 0x0A, 0x0A, 0x1300, 0x1300 },

Package (0x06) { 0x0708, 0x008F90, 0x0A, 0x0A, 0x1200, 0x1200 },

Package (0x06) { 0x06A4, 0x0085E6, 0x0A, 0x0A, 0x1100, 0x1100 },

Package (0x06) { 0x0640, 0x007C71, 0x0A, 0x0A, 0x1000, 0x1000 },

Package (0x06) { 0x05DC, 0x007331, 0x0A, 0x0A, 0x0F00, 0x0F00 },

Package (0x06) { 0x0578, 0x006A25, 0x0A, 0x0A, 0x0E00, 0x0E00 },

Package (0x06) { 0x0514, 0x00614E, 0x0A, 0x0A, 0x0D00, 0x0D00 },

Package (0x06) { 0x04B0, 0x0058AA, 0x0A, 0x0A, 0x0C00, 0x0C00 },

Package (0x06) { 0x044C, 0x005039, 0x0A, 0x0A, 0x0B00, 0x0B00 },

Package (0x06) { 0x03E8, 0x0047FB, 0x0A, 0x0A, 0x0A00, 0x0A00 },

Package (0x06) { 0x0384, 0x003FEE, 0x0A, 0x0A, 0x0900, 0x0900 },

/* Low Frequency Mode */

Package (0x06) { 0x0320, 0x003814, 0x0A, 0x0A, 0x0800, 0x0800 }

})

Method (ACST, 0, NotSerialized)

{

Store ("Method _PR.CPU4.ACST Called", Debug)

Store ("CPU4 C-States : 29", Debug)

/* Low Power Modes for CPU4 */

Return (Package (0x06)

{

One,

0x04,

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000000, // Address

0x01, // Access Size

)

},

One,

Zero,

0x03E8

},

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000010, // Address

0x03, // Access Size

)

},

0x03,

0xCD,

0x01F4

},

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000020, // Address

0x03, // Access Size

)

},

0x06,

0xF5,

0x015E

},

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000030, // Address

0x03, // Access Size

)

},

0x07,

0xF5,

0xC8

}

})

}

Method (_DSM, 4, NotSerialized)

{

Store ("Method _PR.CPU4._DSM Called", Debug)

If (LEqual (Arg2, Zero))

{

Return (Buffer (One)

{

0x03

})

}

Return (Package (0x02)

{

"plugin-type",

One

})

}

}

Scope (\_PR.CPU5)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU5.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

Method (ACST, 0, NotSerialized)

{

Store ("Method _PR.CPU5.ACST Called", Debug)

Store ("CPU5 C-States : 7", Debug)

/* Low Power Modes for CPU5 */

Return (Package (0x05)

{

One,

0x03,

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000000, // Address

0x01, // Access Size

)

},

One,

0x03E8,

0x03E8

},

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000010, // Address

0x03, // Access Size

)

},

0x02,

0x94,

0x01F4

},

Package (0x04)

{

ResourceTemplate ()

{

Register (FFixedHW,

0x01, // Bit Width

0x02, // Bit Offset

0x0000000000000030, // Address

0x03, // Access Size

)

},

0x03,

0xC6,

0xC8

}

})

}

}

Scope (\_PR.CPU6)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU6.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

Method (ACST, 0, NotSerialized) { Return (\_PR.CPU5.ACST ()) }

}

Scope (\_PR.CPU7)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU7.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

Method (ACST, 0, NotSerialized) { Return (\_PR.CPU5.ACST ()) }

}

}

/*

* Intel ACPI Component Architecture

* AML Disassembler version 20140210-00 [Feb 10 2014]

* Copyright (c) 2000 - 2014 Intel Corporation

*

* Original Table Header:

* Signature "SSDT"

* Length 0x0000036A (874)

* Revision 0x01

* Checksum 0x00

* OEM ID "APPLE "

* OEM Table ID "CpuPm"

* OEM Revision 0x00017600 (95744)

* Compiler ID "INTL"

* Compiler Version 0x20140210 (538182160)

*/

DefinitionBlock ("ssdt.aml", "SSDT", 1, "APPLE ", "CpuPm", 0x00017600)

{

External (\_PR.CPU4, DeviceObj)

External (\_PR.CPU5, DeviceObj)

External (\_PR.CPU6, DeviceObj)

External (\_PR.CPU7, DeviceObj)

Scope (\_PR.CPU4)

{

Method (_INI, 0, NotSerialized)

{

Store ("ssdtPRGen version....: 17.6 / Mac OS X 10.11.3 (15D21)", Debug)

Store ("custom mode..........: 0", Debug)

Store ("host processor.......: Intel(R) Core(TM) i5-4670 CPU @ 3.40GHz", Debug)

Store ("target processor.....: i5-4670", Debug)

Store ("number of processors.: 1", Debug)

Store ("baseFrequency........: 800", Debug)

Store ("frequency............: 3400", Debug)

Store ("busFrequency.........: 100", Debug)

Store ("logicalCPUs..........: 4", Debug)

Store ("maximum TDP..........: 84", Debug)

Store ("packageLength........: 31", Debug)

Store ("turboStates..........: 4", Debug)

Store ("maxTurboFrequency....: 3800", Debug)

Store ("machdep.xcpm.mode....: 1", Debug)

}

Name (APLF, Zero)

Name (APSN, 0x04)

Name (APSS, Package (0x1F)

{

/* High Frequency Modes (turbo) */

Package (0x06) { 0x0ED8, 0x014820, 0x0A, 0x0A, 0x2600, 0x2600 },

Package (0x06) { 0x0E74, 0x014820, 0x0A, 0x0A, 0x2500, 0x2500 },

Package (0x06) { 0x0E10, 0x014820, 0x0A, 0x0A, 0x2400, 0x2400 },

Package (0x06) { 0x0DAC, 0x014820, 0x0A, 0x0A, 0x2300, 0x2300 },

/* High Frequency Modes (non-turbo) */

Package (0x06) { 0x0D48, 0x014820, 0x0A, 0x0A, 0x2200, 0x2200 },

Package (0x06) { 0x0CE4, 0x013ADD, 0x0A, 0x0A, 0x2100, 0x2100 },

Package (0x06) { 0x0C80, 0x012DD8, 0x0A, 0x0A, 0x2000, 0x2000 },

Package (0x06) { 0x0C1C, 0x01210F, 0x0A, 0x0A, 0x1F00, 0x1F00 },

Package (0x06) { 0x0BB8, 0x011482, 0x0A, 0x0A, 0x1E00, 0x1E00 },

Package (0x06) { 0x0B54, 0x010831, 0x0A, 0x0A, 0x1D00, 0x1D00 },

Package (0x06) { 0x0AF0, 0x00FC1C, 0x0A, 0x0A, 0x1C00, 0x1C00 },

Package (0x06) { 0x0A8C, 0x00F041, 0x0A, 0x0A, 0x1B00, 0x1B00 },

Package (0x06) { 0x0A28, 0x00E4A0, 0x0A, 0x0A, 0x1A00, 0x1A00 },

Package (0x06) { 0x09C4, 0x00D939, 0x0A, 0x0A, 0x1900, 0x1900 },

Package (0x06) { 0x0960, 0x00CE0B, 0x0A, 0x0A, 0x1800, 0x1800 },

Package (0x06) { 0x08FC, 0x00C316, 0x0A, 0x0A, 0x1700, 0x1700 },

Package (0x06) { 0x0898, 0x00B859, 0x0A, 0x0A, 0x1600, 0x1600 },

Package (0x06) { 0x0834, 0x00ADD4, 0x0A, 0x0A, 0x1500, 0x1500 },

Package (0x06) { 0x07D0, 0x00A387, 0x0A, 0x0A, 0x1400, 0x1400 },

Package (0x06) { 0x076C, 0x009970, 0x0A, 0x0A, 0x1300, 0x1300 },

Package (0x06) { 0x0708, 0x008F90, 0x0A, 0x0A, 0x1200, 0x1200 },

Package (0x06) { 0x06A4, 0x0085E6, 0x0A, 0x0A, 0x1100, 0x1100 },

Package (0x06) { 0x0640, 0x007C71, 0x0A, 0x0A, 0x1000, 0x1000 },

Package (0x06) { 0x05DC, 0x007331, 0x0A, 0x0A, 0x0F00, 0x0F00 },

Package (0x06) { 0x0578, 0x006A25, 0x0A, 0x0A, 0x0E00, 0x0E00 },

Package (0x06) { 0x0514, 0x00614E, 0x0A, 0x0A, 0x0D00, 0x0D00 },

Package (0x06) { 0x04B0, 0x0058AA, 0x0A, 0x0A, 0x0C00, 0x0C00 },

Package (0x06) { 0x044C, 0x005039, 0x0A, 0x0A, 0x0B00, 0x0B00 },

Package (0x06) { 0x03E8, 0x0047FB, 0x0A, 0x0A, 0x0A00, 0x0A00 },

Package (0x06) { 0x0384, 0x003FEE, 0x0A, 0x0A, 0x0900, 0x0900 },

/* Low Frequency Mode */

Package (0x06) { 0x0320, 0x003814, 0x0A, 0x0A, 0x0800, 0x0800 }

})

Method (_DSM, 4, NotSerialized)

{

Store ("Method _PR.CPU4._DSM Called", Debug)

If (LEqual (Arg2, Zero))

{

Return (Buffer (One)

{

0x03

})

}

Return (Package (0x02)

{

"plugin-type",

One

})

}

}

Scope (\_PR.CPU5)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU5.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

}

Scope (\_PR.CPU6)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU6.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

}

Scope (\_PR.CPU7)

{

Method (APSS, 0, NotSerialized)

{

Store ("Method _PR.CPU7.APSS Called", Debug)

Return (\_PR.CPU4.APSS)

}

}

}

굉장히 간략해졌죠? ㅎㅎㅎ

참고로 하나 빼먹은게 있네요 ㅜㅜ

Method (_DSM, 4, NotSerialized)

{

Store ("Method _PR.CPU4._DSM Called", Debug)

If (LEqual (Arg2, Zero))

{

Return (Buffer (One)

{

0x03

})

}

Return (Package (0x02)

{

"plugin-type",

One

})

}

이부분은 씨피유 전력관리 켁스트로 XPCM을 사용하겠습니다라고

알려주는 구문이됩니다만, 실제로 ACST구문에서 xpcm을 사용할지에 대한 여부 옵션이

따로 있는 것으로 알고 있습니다.

P-State만의 패치구문에서 위의 구문은 따로 동작하지 않는것 같으나,

문제가 생길 수 있어 추가로 함께 작성하여 적용하는게 좋다 사료됩니다.

대부분의 C-State은 보드의 바이오스 설정에 들어가면

강제로 설정해줄 수 있는 부분이 되기 때문에,

굳이 SSDT로 패치해주실 필요는 없다 생각됩니다.

이 부분은 다음 하편에서 나올 잠자기에서 그 이유가 매우 자세하게 기술됩니다.

이상으로 마치겠습니다.

감사합니다!

KsJ

KsJ

댓글 15

어쩐지.. 무리하게 잡다가 수치상 스피드스텝은 잘 잡혔는데 잠자기가 안되고 부팅시간도 이상하게 더 늘어나 이상하게 생각하고 있었습니다만, 특히 cpu와 관련된 부분이라서 그런지 무대뽀로 하면 안되겠다는 생각이 확실히 들게 되었습니다. 점점 더 리얼맥에 가까워지네요 ㅎㅎ

여튼 예전에 잘되던 시스템이 갑자기 이상해져서, 클린설치 한 이후에 되도록이면 안건드려줬습니다. 맥에서 잠자기가 두 가지가 있는데 일반절약모드로 잠자기는 가능하지만 최대절전모드로 잠자기가 불가능하여 최대절전모드로 넘어가는 시간을 거의 무한대 값으로 주었습니다. 이렇게 하면 일반절약모드로만 잠자기가 됩니다. 여태까지는 이렇게 해서 일반절약모드로 잠자기를 쓰고 있었는데, 왠지 이 문제를 해결할 수 있을 것 같습니다.

너무 감사합니다.^^ 오늘 저녁에 한번 손봐야겠습니다.

[이런 정보가 술술 나오신다니.... 감동입니다. 저를 조금 더 꼬셔주시면 오즈모시스로 넘어갈 수도 -_-]

질문이 있습니다.

0CE4를 10진수 변환하면? 3300이 나옵니다.

한마디로 3300MHz를 의미합니다.

0x013ADD이 값은 3300Mhz로 동작할때 씨피유가 소모하는

P-state TDP값입니다.

계산방식이 매우 복잡합니다 ;;

우선 자신의 논터보 최고 동작속도의 배율값을 기준으로 잡습니다.

만약 논터보 최고동작속도가 3300이라면 33, 3500이라면 35로합니다.

그리고 자신이 계산하려고 하는 씨피유의 동작속도의 배율을 빼줍니다.

위 경우는 34에서 33을 빼주므로 1이됩니다.

이 1에다 0.00625를 곱해줍니다.

34를 기준으로 하여 8~33까지 계산은 잘 이해가 되었습니다.

만약에 34 이상의 값을 적어줄 때도 계산이 동일한가요?

34로 계산할 경우 34-34 =0 이 되고

35로 계산할 경우 34-35 = -1이 되는데

이럴 때 어떻게 계산을 하신건지 궁금합니다.

해당 씨피유가 지원하는 터보부스트의 시작 주파수부터 (제경우 3400부터)는 계산식이 안들어가고

맥스 TDP * 1000한 값을 16진수로 환산하여 사용하게됍니다 :)

아아, 그렇군요. 결국 TDP도 모델마다 다른거니... 작업하고 제가 쓰는 모델에 대해 공유해놔야 할 것 같아요.

C-State부분 (ACST) 은 미적용하시는걸 추천드려요. 레이턴시가 파이커 아저씨 맘대로 (?) 해둔거라서 시스템에 안맞아 불균형을 초래할 수 있거든요.

감사합니다. 현재상황 보고하면

공학용계산기에 식 세우고 8~34까지 전부 계산해주었습니다. 일단 이 구간 안에 tdp값을 곱한 값들은 모두 구해놓았습니다.ㅋㅋ

현재 제 SSDT에 보니 이상한 점이 있습니다.

0x00014820 (TDP*1000=84000)이렇게 표시가 되었군요.

KsJ님 ssdt를 보니 0x014820으로 표기가 되어있는데, 어떤 표기 방법을 따라야 하는 것인가요?

x 바로 뒤에 있는 0은 상관이 없는 것인지... 잘모르겠습니다.

4자리, 6자리, 2자리, 2자리, 4자리, 4자리 랄까요?

3

3

2

2

좋은 자료 감사합니다.